## SISTEMAS DIGITAIS

# Licenciatura em Engenharia Eletrotécnica Licenciatura em Engenharia Informática

Exame (1ª Chamada) – 24 de janeiro de 2019

- · Apenas é permitido ter em cima da mesa de exame os enunciados e folhas entregues pelo docente.

- · A cotação das perguntas encontra-se indicada, no fim das mesmas, entre parêntesis retos.

- · O aluno detetado a plagiar verá o seu exame anulado e poderá incorrer em processo disciplinar.

Duração da prova: 1 hora e  $\frac{1}{2}$ .

1- O 74LS112 é um circuito integrado da família TTL que contém dois flip-flop's JK ativos à transição descendente com entradas de CLEAR e PRESET assíncronas. Explique como essas duas entradas condicionam o funcionamento do flip-flop indicando o significado destas serem assíncronas e como isso se reflete no funcionamento do flip-flop e no projeto de contadores assíncronos. [3]

R:

No 74LS112, um circuito integrado frequentemente utilizado nos trabalhos laboratoriais, possui, no mesmo encapsulamento DIP16, dois flip-flops JK independentes, ativos à transição descendente, com entradas de clear e preset assíncronas e ativas ao valor lógico baixo. Estas últimas duas entradas, sendo assíncronas, significa que quando ativadas o comportamento do flip-flop é alterado independentemente do sinal de clock. Ou seja, quando se coloca a entrada clear = 0, a saída Q do flip-flop correspondente é forçada a ser zero independentemente do estado do sinal de clock. Por outro lado, se preset=0, a saída Q do flip-flop é forçada a ir a 1. (mais detalhes acerca do funcionamento os flip-flop's podem ser obtidos pela análise das folhas de dados do componente disponível em 74LS112). Dado que as entradas de clear e preset são assíncronas, ao contrário das entradas J e K, o projeto de um contador assíncrono requer a utilização de um estado "intermédio" no caso de ser necessário alterar a normal sequencia de contagem do contador. Por exemplo, um contador assíncrono de 2 bits para contar pelos valores 1,2,3,1,... requer que, ao chegar a 3, o estado seguinte seja O e a alteração das entradas de clear e preset serão atualizadas nesse estado "intermédio".

**2-** Considere a seguinte tabela de verdades:

| Α | В | С | D | F(A,B,C,D) |

|---|---|---|---|------------|

| 0 | 0 | 0 | 0 | 1          |

| 0 | 0 | 0 | 1 | 0          |

| 0 | 0 | 1 | 0 | 0          |

| 0 | 0 | 1 | 1 | 1          |

| 0 | 1 | 0 | 0 | 0          |

| 0 | 1 | 0 | 1 | 1          |

| 0 | 1 | 1 | 0 | 1          |

| 0 | 1 | 1 | 1 | 0          |

| 1 | 0 | 0 | 0 | 0          |

| 1 | 0 | 0 | 1 | 1          |

| 1 | 0 | 1 | 0 | 1          |

| 1 | 0 | 1 | 1 | 0          |

| 1 | 1 | 0 | 0 | 1          |

| 1 | 1 | 0 | 1 | 0          |

| 1 | 1 | 1 | 0 | 0          |

| 1 | 1 | 1 | 1 | 1          |

a) Obtenha a forma canónica conjuntiva desta tabela de verdades e mostre, recorrendo ao mapa de Karnaugh, que a forma canónica coincide com a forma mais simples. [2] R:

A obtenção da forma canónica conjuntiva a partir de uma tabela de verdades passa por escolher, na tabela de verdades, todos os maxterm. Ou seja, a combinação de valores das entradas que se traduzem numa saída igual a zero. Em cada termo, todas as variáveis de entrada são consideradas: ou na forma normal ou negada. Uma variável toma o valor negado se o valor que lhe está associado, nas colunas das variáveis independentes, é 1 e entra na forma normal se o valor que lhe está associado é 0. Assim, a forma canónica pedida tem a seguinte forma:

$$F(A, B, C, D) = (A + B + C + \overline{D}). (A + B + \overline{C} + D). (A + \overline{B} + C + D). (A + \overline{B} + \overline{C} + \overline{D}). (\overline{A} + B + C + D). (\overline{A} + B + \overline{C} + \overline{D}). (\overline{A} + \overline{B} + C + \overline{D}). (\overline{A} + \overline{B} + \overline{C} + \overline{D})$$

Utilizando a mesma tabela de verdades no preenchimento do mapa de Karnaugh obtém-se:

Verifica-se que só é possível fazer grupos de um elemento. Sabemos por isso que a expressão final irá coincidir com a forma canónica. Como queremos comparar com a forma canónica conjuntiva, começamos por selecionar os "zeros" no mapa de Karnaugh escrevendo, de seguida, a expressão lógica de acordo com as regras aprendidas durante as AULAS!.

| AB |    |    |    |    |

|----|----|----|----|----|

| CD | 00 | 01 | 11 | 10 |

| 00 | 1  | 0  | 1  | 0  |

| 01 | 0  | 1  | 0  | 1  |

| 11 | 1  | 0  | 1  | 0  |

| 10 | 0  | 1  | 0  | 1  |

De onde se tira que:

$$F(A, B, C, D) = (A + B + C + \overline{D}). (A + B + \overline{C} + D). (A + \overline{B} + C + D). (A + \overline{B} + \overline{C} + \overline{D}). (\overline{A} + B + C + D). (\overline{A} + B + \overline{C} + \overline{D}). (\overline{A} + \overline{B} + C + \overline{D}). (\overline{A} + \overline{B} + \overline{C} + \overline{D})$$

Como ambas as expressões são idênticas, prova-se então que a forma canónica é a forma mais simples possível. Isso não significa que sejam precisas tantas portas lógicas para a implementação deste circuito. Vimos nas AULAS que é possível fatorizar algumas operações que são realizadas mais do que uma vez reduzindo assim o número de portas lógicas necessárias. Por exemplo, o termo A+B aparece duas vezes assim como outros...

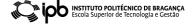

b) Utilizando um multiplexador 8:1 projete um circuito digital que represente esta função (para além do multiplexador, utilize as operações lógicas que achar necessárias). [2] R:

Mais uma vez, como vimos nas AULAS, uma função lógica combinatória arbitrária pode ser implementada recorrendo a multiplexadores. Neste caso é pedido o uso de um multiplexador 8:1 o que significa que este dispositivo tem apenas três entradas de controlo. Havendo 4 variáveis independentes, uma delas será introduzida no sistema a partir das 8 entradas de dados. O algoritmo estudado para implementar esta solução é bastante simples. Começa-se por fazer grupos de duas linhas consecutivas. Um detalhe interessante é que, em cada um desses grupos, as variáveis A, B e C não mudam de valor. Serão essas variáveis que estarão associadas às entradas de controlo. Neste caso vamos assumir que a entrada de

controlo MAIS SIGNIFICATIVA está associada à variável A e a menos significativa à C. Assim, obtém-se:

| Α | В | С | D | F(A,B,C,D) |               |

|---|---|---|---|------------|---------------|

| 0 | 0 | 0 | 0 | 1          | F(A,B,C,D)=D' |

| 0 | 0 | 0 | 1 | 0          |               |

| 0 | 0 | 1 | 0 | 0          | F(A;B;C;D)=D  |

| 0 | 0 | 1 | 1 | 1          |               |

| 0 | 1 | 0 | 0 | 0          | F(A;B;C;D)=D  |

| 0 | 1 | 0 | 1 | 1          |               |

| 0 | 1 | 1 | 0 | 1          | F(A,B,C,D)=D' |

| 0 | 1 | 1 | 1 | 0          |               |

| 1 | 0 | 0 | 0 | 0          | F(A;B;C;D)=D  |

| 1 | 0 | 0 | 1 | 1          |               |

| 1 | 0 | 1 | 0 | 1          | F(A;B;C;D)=D' |

| 1 | 0 | 1 | 1 | 0          |               |

| 1 | 1 | 0 | 0 | 1          | F(A;B;C;D)=D' |

| 1 | 1 | 0 | 1 | 0          |               |

| 1 | 1 | 1 | 0 | 0          | F(A;B;C;D)=D  |

| 1 | 1 | 1 | 1 | 1          |               |

### O esquema final fica:

3- A adição de um bit de paridade é uma técnica muito utilizada na transmissão de informação no formato digital a fim do recetor ser capaz de detetar se ocorreu ou não um erro. É o caso de muitos protocolos de comunicação série assíncronos onde, para além dos bits de mensagem e de controlo, é acrescentado um bit de paridade. O bit de

paridade é '1' se o número de bits a '1' da mensagem for ímpar e '0' se for par. Por exemplo, se a mensagem de 8 bits a transmitir for '00010000' então o bit de paridade é '1'. Por outro lado, se fosse '10010000', o bit de paridade seria '0'. Note que, se o número de bits a '1' for nulo (ou seja, caso se trate do binário '0'), a paridade do mesmo será '1'. Projete um circuito **combinatório** que, dada uma mensagem de **4 bits**, este seja capaz de determinar automaticamente o seu bit de paridade. Para isso deve:

I. Obter a tabela de verdades; [2]

R:

| B3 | B2 | B1 | B0 | PARIDADE (P) |

|----|----|----|----|--------------|

| 0  | 0  | 0  | 0  | 1            |

| 0  | 0  | 0  | 1  | 1            |

| 0  | 0  | 1  | 0  | 1            |

| 0  | 0  | 1  | 1  | 0            |

| 0  | 1  | 0  | 0  | 1            |

| 0  | 1  | 0  | 1  | 0            |

| 0  | 1  | 1  | 0  | 0            |

| 0  | 1  | 1  | 1  | 1            |

| 1  | 0  | 0  | 0  | 1            |

| 1  | 0  | 0  | 1  | 0            |

| 1  | 0  | 1  | 0  | 0            |

| 1  | 0  | 1  | 1  | 1            |

| 1  | 1  | 0  | 0  | 0            |

| 1  | 1  | 0  | 1  | 1            |

| 1  | 1  | 1  | 0  | 1            |

| 1  | 1  | 1  | 1  | 0            |

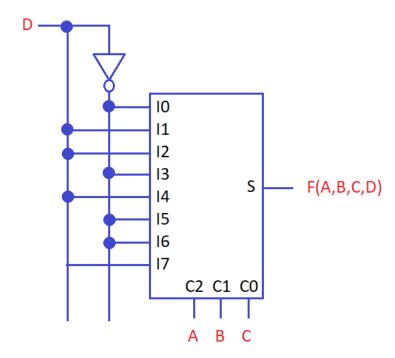

II. Derivar as equações lógicas que relacionam a saída com as entradas; [2]R:

O número de expressões lógicas de um determinado circuito lógico combinatório é igual ao número de variáveis dependentes. Neste caso, havendo apenas P como variável dependente, apenas uma equação será necessária. Como é obvio, pretendemos a expressão lógica mais simples possível pelo que iremos recorrer ao mapa de Karnaugh:

$$\begin{split} P &= \overline{B}_3 \cdot \overline{B}_2 \cdot \overline{B}_1 + \overline{B}_3 \cdot \overline{B}_1 \cdot \overline{B}_0 + \overline{B}_2 \cdot \overline{B}_1 \cdot \overline{B}_0 + \overline{B}_3 \cdot \overline{B}_2 \cdot \overline{B}_0 + \overline{B}_3 \cdot \overline{B}_2 \cdot B_1 \cdot B_0 + B_3 \cdot \overline{B}_2 \cdot B_1 \cdot B_0 + B_3 \cdot \overline{B}_2 \cdot B_1 \cdot \overline{B}_0 + B_3 \cdot \overline{B}_2 \cdot \overline{B}_1 \cdot \overline{B}_0 + B_3 \cdot \overline{B}_2 \cdot \overline{B}_1 \cdot \overline{B}_0 + B_3 \cdot \overline{B}_2 \cdot \overline{B}_1 \cdot \overline{B}_0 \end{split}$$

Que pode, opcionalmente, ser reescrita como:

$$\begin{split} P &= \overline{B}_3 \cdot \overline{B}_2 \cdot \left(\overline{B}_1 + \overline{B}_0\right) + \left(\overline{B}_3 + \overline{B}_2\right) \cdot \overline{B}_1 \cdot \overline{B}_0 + \left(\overline{B}_3 \cdot B_2 + B_3 \cdot \overline{B}_2\right) B_1 \cdot B_0 + B_3 \cdot B_2 \cdot \left(\overline{B}_1 \cdot B_0 + B_1 \cdot \overline{B}_0\right) \\ &= \overline{B}_3 \cdot \overline{B}_2 \cdot \left(\overline{B}_1 + \overline{B}_0\right) + \overline{B}_1 \cdot \overline{B}_0 \cdot \left(\overline{B}_3 + \overline{B}_2\right) + B_1 \cdot B_0 \cdot \left(B_3 \oplus B_2\right) + B_3 \cdot B_2 \cdot \left(B_1 \oplus B_0\right) \end{split}$$

#### Nota:

Observem que esta expressão pode ser ainda tornada mais compacta. De facto, se repararem bem para a tabela de verdades podem verificar que, com exceção da primeira linha, o resultado do bit de paridade não é mais do que o resultado da soma módulo 2 dos quatro bits de entrada. Assim, a expressão anterior pode ser obtida por:

$$P = (B_3 \oplus B_2 \oplus B_1 \oplus B_0) + (\overline{B}_3 \cdot \overline{B}_2 \cdot \overline{B}_1 \cdot \overline{B}_0)$$

Como sugestão, verifiquem expandindo esta expressão, que se trata da mesma igualdade obtida anteriormente. Neste caso, o diagrama lógico é bastante simples como podem perceber.

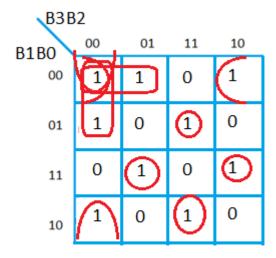

#### III. Desenhar o diagrama lógico. [2]

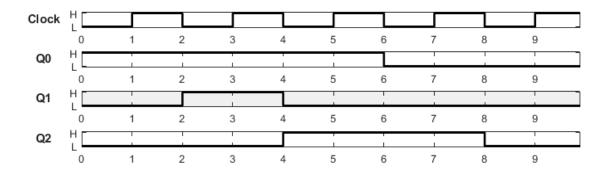

**4-** O diagrama temporal representado em baixo descreve o comportamento de um circuito sequencia síncrono constituído por 3 flip-flop's tipo **D** ativos à transição **descendente**. Considere que a sequência de saídas desses flip-flop's se repete indefinidamente.

a) Considerando que a ordem de significância dos bits à saída do contador aumenta com o índice associado à letra Q (ou seja, Q<sub>0</sub> representa o LSB e Q<sub>2</sub> o MSB), indique qual é a sequência de contagem. [1]

R:

Mais uma vez, e para quem esteve presente nas AULAS, quando se falou em contadores foi referido, e feito exemplos no quadro, que tipicamente o valor da sequência de contagem não é mais do que o equivalente na base 10 da sequência de bits composta pelos valores à saída dos flip-flop's. Como é obvio, esse valor depende de qual dos bits é considerado o mais significativo e o menos significativo. Neste caso, é referido que a significância aumenta com o valor do índice. Por isso Q2

fornece o bit mais significativo e Q0 o menos significativo. Inicialmente a sequência de valores para Q2 Q1 Q0 é "0 0 1" e, a cada transição descendente do sinal de clock, os valores passam por: "0 1 1", "1 0 1", "1 0 0", "0 0 0". Em decimal, a sequencia de contagem é portanto 1,3,5,4,0 que se repete indefinidamente.

- b) Projete o circuito digital que seja capaz de produzir as ondas do diagrama temporal acima ilustrado. Para isso deve:

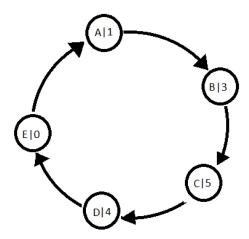

- I. Desenhar o diagrama de estados do contador; [1]

De forma a simplificar o desenho do contador, e dado que todos os valores de saída são distintos, aconselha-se a seguinte atribuição de estados:

A - 001

B - 011

C - 101

D - 100

E - 000

II. Preencher a tabela de transição de estados; [2]

R:

| Estados Presentes | Estados Seguintes |          | Saídas   |

|-------------------|-------------------|----------|----------|

| Q2 Q1 Q0          | Q2 Q1 Q0          | D2 D1 D0 | S2 S1 S0 |

| 000               | 001               | 001      | 000      |

| 001               | 011               | 011      | 001      |

| 010               | XXX               | XXX      | XXX      |

| 011               | 101               | 101      | 011      |

| 100               | 000               | 000      | 100      |

| 101               | 100               | 100      | 101      |

| 110               | XXX               | XXX      | XXX      |

| 111               | XXX               | XXX      | XXX      |

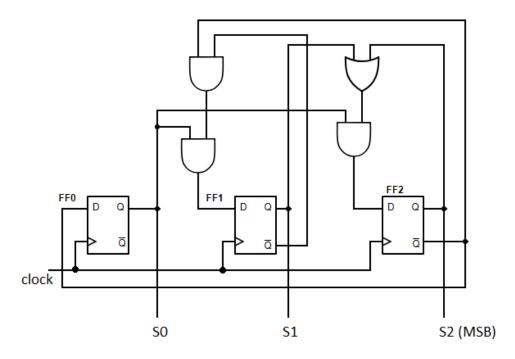

III. Obter as equações de excitação; [2]

<u>D2</u>

| Q2 Q1<br>Q0 | 00 | 01 | 11 | 10 |

|-------------|----|----|----|----|

| 0           | 0  | х  | x  | 0  |

| 1           | 0  | 1  | x  | 1  |

|             |    |    |    |    |

D2 = Q1.Q0 + Q2.Q0 = Q0.(Q1 + Q2)

<u>D1</u>

| Q2 Q1<br>Q0 | 00 | 01 | 11 | 10 |

|-------------|----|----|----|----|

| 0           | 0  | х  | х  | 0  |

| 1           | 1  | 0  | х  | 0  |

D1=Q2'.Q1'.Q0

<u>D0</u>

| Q2 Q1<br>Q0 | 00 | 01 | 11 | 10 |

|-------------|----|----|----|----|

| 0           | 1  | x  | ×  | 0  |

| 1           | 1  | 1  | х  | 0  |

D0=Q2'

IV. Desenhar o diagrama lógico do contador; [1]

R:

Considere "don't care" o comportamento da máquina fora dos estados utilizados.

## FIM DA PROVA